I know FTB is more than just one mod, but redpower has all but died on the mc forums. heres hoping some people here still appreciate all the work that went into this fantastic component and post some of their crazy ideas here.

here goes =)

working on some components for a redpower cpu build, here's a pc counter register design i came up with

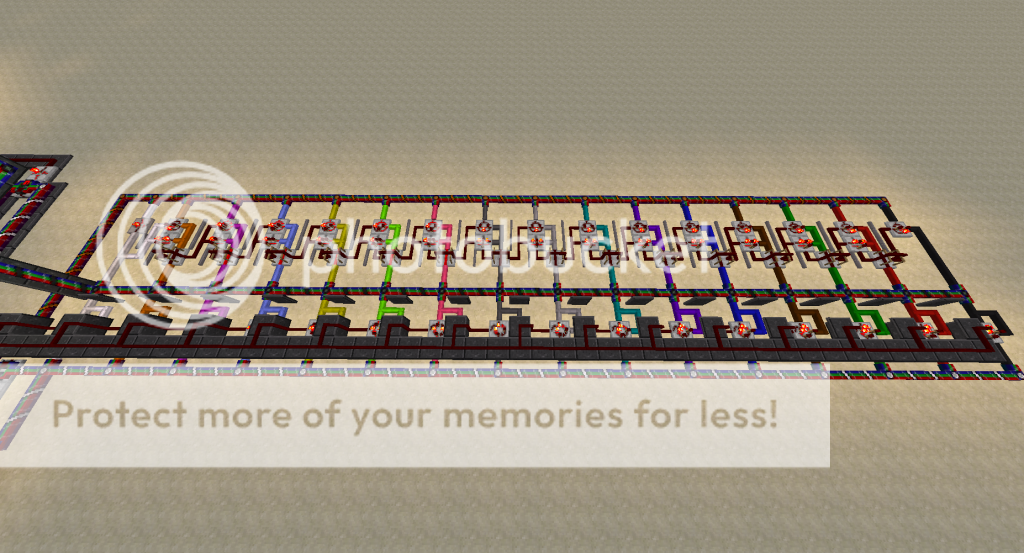

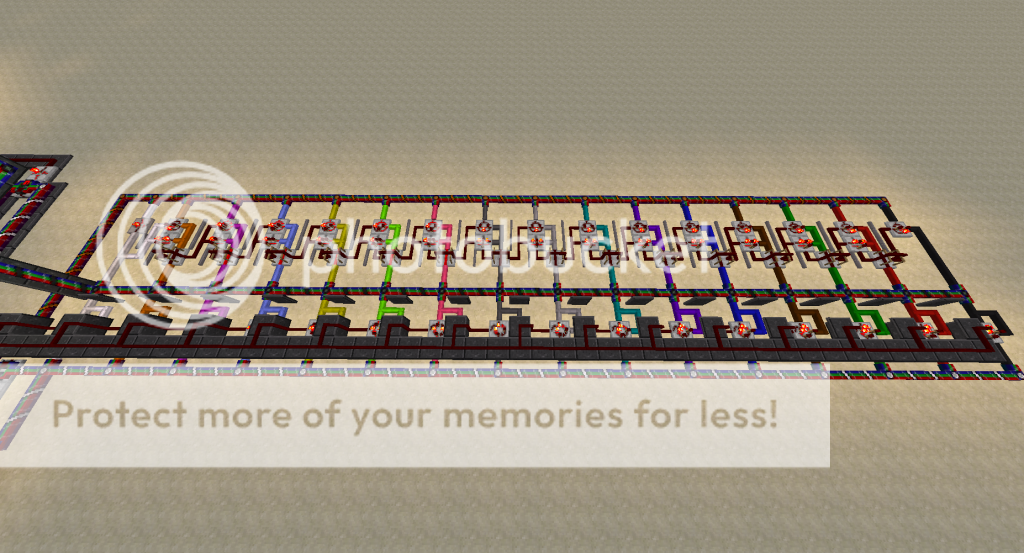

this shows the dff's and adders for the +1 logic. note i dont need full adder logic here since we are only adding 1 to the value on the output bus on the lsb...the rest of the bits are adding 0, so we only have to add the incoming carry and pass the resulting carry to next bit. i know...ripple carry, slow as balls. will fix later =p

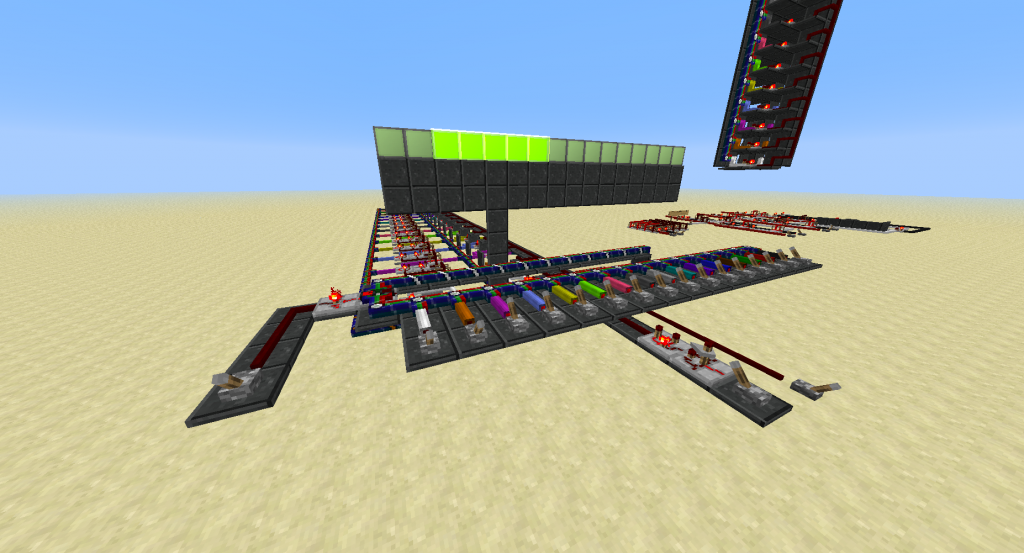

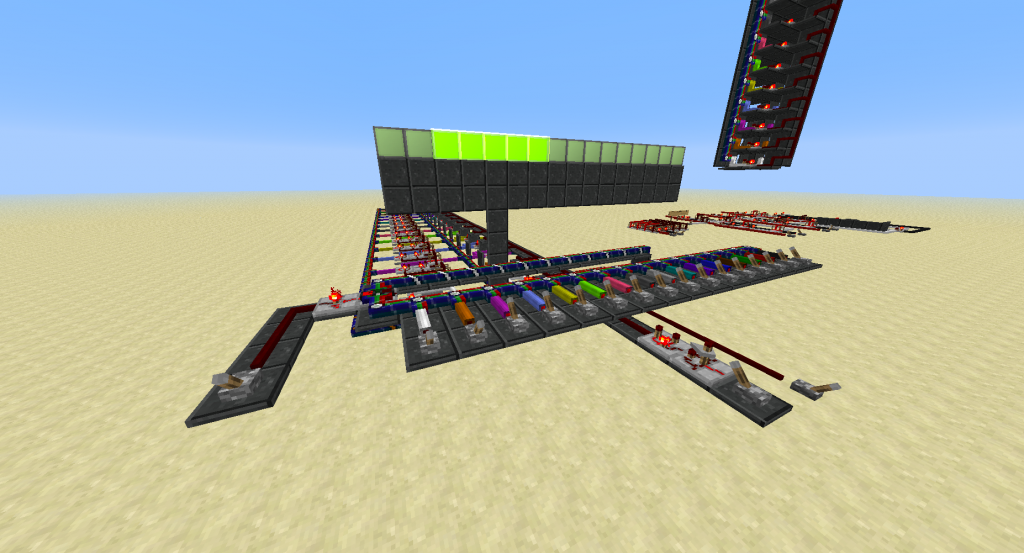

here is the countup/load address selector. just a couple of bus transceivers that select which data bus gets fed into the dff's

input section.

leftmost switch = reset to 0 (edit: this is actually linked to the last switch to force the register into load mode, i forgot that little detail)

bank of 16 switches = input bits to load into register

switch with clock/pulse former = clock signal, clock tile is there to test the counting of the register, otherwise it should just be the pulse former

rightmost switch = countup/load address toggle

its not terribly fast because of the ripple adder circuit..looking into CLA designs to speed this up..right now it needs ~40 ticks (2 seconds) on large numbers. can be much faster if only handling smaller numbers. one cool feature of this design is the countup logic does its thing AFTER the previous value is clocked into the DFF's. so it is slow to figure out the next address, but the rest of the system can do its thing while the counter is running the +1 on the current address. It might be a moot idea to speed this up if the rest of the computer takes more than 40 ticks to run one instruction. clocking in a new address from the load bits only takes a few ticks.

here goes =)

working on some components for a redpower cpu build, here's a pc counter register design i came up with

this shows the dff's and adders for the +1 logic. note i dont need full adder logic here since we are only adding 1 to the value on the output bus on the lsb...the rest of the bits are adding 0, so we only have to add the incoming carry and pass the resulting carry to next bit. i know...ripple carry, slow as balls. will fix later =p

here is the countup/load address selector. just a couple of bus transceivers that select which data bus gets fed into the dff's

input section.

leftmost switch = reset to 0 (edit: this is actually linked to the last switch to force the register into load mode, i forgot that little detail)

bank of 16 switches = input bits to load into register

switch with clock/pulse former = clock signal, clock tile is there to test the counting of the register, otherwise it should just be the pulse former

rightmost switch = countup/load address toggle

its not terribly fast because of the ripple adder circuit..looking into CLA designs to speed this up..right now it needs ~40 ticks (2 seconds) on large numbers. can be much faster if only handling smaller numbers. one cool feature of this design is the countup logic does its thing AFTER the previous value is clocked into the DFF's. so it is slow to figure out the next address, but the rest of the system can do its thing while the counter is running the +1 on the current address. It might be a moot idea to speed this up if the rest of the computer takes more than 40 ticks to run one instruction. clocking in a new address from the load bits only takes a few ticks.